# logicBRICKS logiHSSL High Speed Serial Link (HSSL) Slave Controller

November 16, 2021

.

Data Sheet

**Core Facts**

Documentation

Design File Formats Constraints Files

Reference Designs &

and Aldec Active-HDL<sup>™</sup>

Support provided by Xylon

Application Notes

Additional Items

Provided with Core

User's Manual Encrypted VHDL

**Supported Simulation Tools**

Support

Mentor Graphics ModelSim®, QuestaSim®

Reference design constraint files

logiHSSL-ZU starter kit

Reference design prepared for the

logiHSSL-ZU FPGA HSSL Starter Kit

Version: v1.2

| Xylon d.o.o.           |                         |  |  |  |

|------------------------|-------------------------|--|--|--|

| Fallerovo setaliste 22 |                         |  |  |  |

| 10000 Zagreb, Croatia  |                         |  |  |  |

| Phone:                 | +385 1 368 00 26        |  |  |  |

| Fax:                   | +385 1 365 51 67        |  |  |  |

| E-mail:                | support@logicbricks.com |  |  |  |

| URL:                   | www.logicbricks.com     |  |  |  |

# **Features**

. . .

- Supports Xilinx<sup>®</sup> 7 Series, UltraScale<sup>™</sup> and UltraScale+<sup>™</sup> FPGAs, Zynq<sup>®</sup>-7000 SoC and UltraScale+ Zynq MPSoC device families

- Slave controller IP core compatible with the High Speed Serial Link (HSSL) native interface from Infineon Technologies AG

- Aimed at safety-critical automotive applications

- Enables easy interfacing between Infineon's AURIX™ TC2xx and TC3xx microcontrollers and Xilinx FPGA and SoC/MPSoC devices

- Low pin count (2 x 2 LVDS, 1 x clock)

- Supports baud rates of up to 320 Mbaud/s at a net payload data-rate of up to 84%

- HSSL Sleep function is not supported

- Optional debug ports for debugging during system integration

- Implements ARM<sup>®</sup> AMBA<sup>®</sup> AXI4–Lite Slave bus compliant interface and enables easy access to internal registers inside the logiHSSL IP

- Implements ARM AMBA AXI4 Master bus compliant interface that enables logiHSSL IP an easy access to 3 GB of local Xilinx device addressable space (from 0x00000000 to 0xBFFFFFFF). This enables AURIX microcontroller to access:

- Registers and on-chip RAM in programmable logic (access to internal register spaces of other IPs)

- Register space and On-Chip Memory (OCM) in the processing system through High priority ports.

- On-board linearly addressable Flash memory

- On-board DDR memory through local memory controllers

- logiHSSL-ZU FPGA HSSL Starter Kit is available from Xylon

- Prepared for the Xilinx Vivado® Design Suite

# Table 1: Example Implementation Statistics for Xilinx<sup>®</sup> FPGAs

| Family<br>(Device)                         | Fmax<br>(MHz) | LUT <sup>1)</sup> | FF <sup>1)</sup> | IOB | СМТ | BRAM | MULT/<br>DSP48/E | DCM /<br>CMT | GTx | Design<br>Tools |

|--------------------------------------------|---------------|-------------------|------------------|-----|-----|------|------------------|--------------|-----|-----------------|

| Zynq <sup>®</sup> -7000<br>(xc7z045ffg900) | 80            | 9204              | 6503             | 0   | 0   | 0    | 0                | 0            | 0   | Vivado 2021.2   |

| Zynq® UltraScale+™<br>(xczu9eg-ffvb1156-2) | 80            | 9077              | 6496             | 0   | 0   | 0    | 0                | 0            | 0   | Vivado 2021.2   |

1. Assuming configuration: No debug ports. No separate AXI clock.

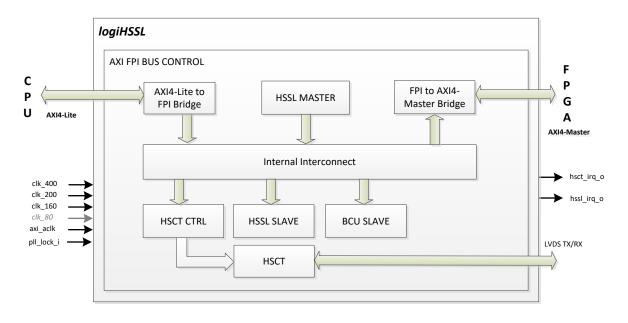

Figure 1: logiHSSL Architecture

## Applications

Emerging automotive and industrial applications, such as the Advanced Driver Assistance (ADAS) and Automated Driving (AD), are both performance hungry and safety-critical. Typically the supporting system architectures use the Xilinx FPGA and SoC devices for data aggregation, pre-processing and data distribution tasks, and the Infineon AURIX microcontrollers to provide the ASIL D level functional safety.

### **General Description**

The logiHSSL IP core enables high-speed communication between microcontrollers of Infineon's AURIX family (TC2xx and TC3xx) and Xilinx SoC (System-on-Chip), MPSoC (Multi-Processor SoC) and FPGA (Field Programmable Gate Arrays) devices, via the Infineon High Speed Serial Link (HSSL). This serial link supports baudrates of up to 320 Mbaud at a net payload data-rate of up to 84%.

The new IP core allows system designers to combine functional safety and security provided by AURIX with the wide range of functional possibilities brought to the table by the Xilinx devices. Linked devices can access and control each other's internal and connected resources through the HSSL link. The logiHSSL IP is prepared for the Xilinx Vivado Design Suite to enable quick and efficient implementation in the latest Xilinx All Programmable devices, for use in the embedded systems that meet the highest safety standards.

### **Functional Description**

The logiHSSL IP core is an IP block for the Xilinx Vivado development flow. It includes the embedded Infineon High Speed Serial Interface (HSSL) and a control unit to connect an external Infineon AURIX automotive microcontroller with a Xilinx FPGA and/or ARM processing unit (SoC, MPSoC) for the purpose of the data exchange.

Five major modules can be identified in the architectural block diagram shown in Figure 1.

### **HSCT Layer**

The HSCT layer is the implementation of the HSCT link layer. It is the physical layer of the HSSL protocol.

### **HSSL Control Unit**

The HSSL control unit is the IP core's main module that facilitates the control over the HSSL protocol, which includes the HSSL layer (upper layer) and HSCT layer (lower layer). The control is interfaced to the CPU by means of a register set. There are separate register sets for HSSL and HSCT layer control.

#### Internal Interconnect

Internal interconnect is a bus architecture that connects all units within the IP core.

#### AXI4–Lite Interface (Slave)

AXI4–Lite slave interface is used to access all IP core's registers within the HSSL control unit. It facilitates a bridge from the AXI4–Lite bus to the internal interconnect.

#### AXI4 Interface (Master)

IP core can access any AXI-addressable space in the FPGA/SoC/MPSoC through the AXI4 master interface. It facilitates a bridge from the internal interconnect to the AXI4 bus architecture, including the corresponding address remapping.

For more information on internal architecture of the HSSL protocol control (HSCT layer and HSSL control unit), as well as on the internal interconnect architecture, see AURIX TC27x C-Step 32-Bit Single-Chip Microcontroller documentation from <u>Infineon</u>.

### Core I/O Signals

### Table 2: Core I/O Signals

| Signal                  | Signal<br>Direction | Description                                                                                    |

|-------------------------|---------------------|------------------------------------------------------------------------------------------------|

| AXI4 - Master Interface | Bus                 | Refer to ARM AMBA AXI4 specification*                                                          |

| AXI4 - Lite Interface   | Bus                 | Refer to ARM AMBA AXI4 specification*                                                          |

| clk_400                 | Input               | 400 MHz clock used for sampling of the HSSL RX lines*                                          |

| rst_400                 | Input               | 400 MHz reset                                                                                  |

| clk_200                 | Input               | 200 MHz clock used for sampling of the HSSL RX lines*                                          |

| rst_200                 | Input               | 200 MHz reset                                                                                  |

| clk_160                 | Input               | 160 MHz clock used for data output on the HSSLTX lines*                                        |

| clk_80                  | Input               | 80 MHz clock used for RX/TX logic**                                                            |

| rst_80                  | Input               | 80 MHz reset**                                                                                 |

| hsct_irq_o              | Output              | HSCT interrupt signal                                                                          |

| hssl_irq_o[15:0]        | Output              | HSSL interrupt pulse signals                                                                   |

| lvdsrx_data_p           | Input               | LVDS HSSL serial input, positive                                                               |

| lvdsrx_data_n           | Input               | LVDS HSSL serial input, negative                                                               |

| lvdstx_data_p           | Output              | LVDS HSSL serial output, positive                                                              |

| lvdstx_data_n           | Output              | LVDS HSSL serial output, negative                                                              |

| pll_lock_i              | Input               | PLL lock signal – lock detection. Indicates the state of the PLL within the<br>clocking logic. |

| dbg_slv_txen            | Output              | Debug output – internal TX enable (80 MHz).                                                    |

| dbg_lvdstx_smpl         | Output              | Debug output – internal TX data bus (80 MHz).                                                  |

| dbg_slv_clktsten        | Output              | Debug output – internal TX clock test enable (80 MHz).                                         |

| dbg_slv_loopen          | Output              | Debug output – internal loop RX->TX enable (80 MHz).                                           |

| dbg_lvdsrx_smpl         | Output              | Debug output – internal RX sample data bus (1600 Mbps, 80 MHz clock).                          |

| dbg_rx_low_speed        | Output              | Debug output – internal RX low speed active (80 MHz).                                          |

| dbg_rx_high_speed       | Output              | Debug output – internal RX high speed active (80 MHz).                                         |

| dbg_rx_ph_val           | Output              | Debug output – internal RX phase valid detected (80 MHz).                                      |

| dbg_rx_ph_act           | Output              | Debug output – internal RX phase active (80 MHz).                                              |

| dbg_rx_data             | Output              | Debug output – internal RX data byte (input to data stream processing) (80                     |

Copyright © Xylon d.o.o. 2001-2021 All Rights Reserved

### logiHSSL Slave HSSL Controller

| Signal          | Signal<br>Direction | Description                                                                                                                               |  |  |

|-----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 |                     | MHz).                                                                                                                                     |  |  |

| dbg_rx_data_val | Output              | Debug output – internal RX data byte valid strobe (input to data stream processing, asserted for 1 clock on each byte received) (80 MHz). |  |  |

\* If separate AXI clock is not enabled, AXI4 Master and AXI4-lite Slave interfaces must work on 80 MHz clock, generated from the same clock source as the 160 MHz clock used for HSSL TX, as well as 400 MHz and 200 MHz clocks used for HSSL RX. It is preferred to use the clock reference from the HSSL Master. If using separate AXI clock, it has to be faster than 40 MHz. \*\* Present only if separate AXI clock is enabled. Must be generated from the same clock source as the 160 MHz clock used for HSSL

TX, as well as 400 MHz and 200 MHz clocks used for HSSL RX. It is preferred to use the clock reference from the HSSL Master.

## **Verification Methods**

The logiHSSL is fully supported by the Xilinx Vivado (IPI) Design Suits. This tight integration tremendously shortens IP integration and verification. A full logiHSSL implementation does not require any particular skills beyond general Xilinx tools knowledge. For more information, please contact Xylon Technical Support:

Email: <u>support@logicbricks.com</u>

## **Recommended Design Experience**

The user should have experience in the following areas:

- Xilinx design tools

- ModelSim

## **Available Support Products**

To jump-start new designs that combine the Infineon's AURIX microcontrollers with the Xilinx All Programmable FPGA and SoC devices and solve the rising safety and performance requirements in emerging automotive and industrial designs, Xylon offers the complete logiHSSL-ZU FPGA HSSL Starter Kit. The kit includes the complete hardware platform built from the Xilinx UltraScale+ MPSoC based ZCU104 Evaluation Kit and the Infineon AURIX Evaluation board with the necessary cabling. Additionally, it comes with the fully functional reference hardware design. To learn more about this product, please contact Xylon or visit our web site:

Email:

sales@logicbricks.com

URL:

https://www.logicbricks.com/Products/logiHSSL-ZU.aspx

# **Ordering Information**

This product is available directly from Xylon under the terms of the Xylon's IP License. Please visit our web shop or contact Xylon for pricing and additional information:

Email: <u>sales@logicbricks.com</u> URL: <u>www.logicbricks.com</u>

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. Xylon products are not intended for use in the life support applications. Use of the Xylon products in such appliances is prohibited without written Xylon approval.

# **Related Information**

### Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

### Infineon AURIX/TriBoard and HSSL

Infineon Technologies AG Am Campeon 1 – 15 85579 Neubiberg, Germany URL: <u>www.infineon.com</u>

### **Revision History**

| Version | Date        | Note                                            |  |  |  |  |

|---------|-------------|-------------------------------------------------|--|--|--|--|

| 1.00.   | 08.05.2019. | Initial Xylon release.                          |  |  |  |  |

| 1.01.   | 07.02.2020. | New physical layer, optimized for Xilinx FPGAs. |  |  |  |  |

|         |             | Removed separate clock for AXI4-Lite Slave.     |  |  |  |  |

| 1.02.   | 15.03.2021. | Removed reference clock. Added debug ports.     |  |  |  |  |

|         |             | Optimized design.                               |  |  |  |  |

|         | 16.11.2021. | Updated for Vivado 2021.2.                      |  |  |  |  |

Xylon d.o.o. – Fallerovo setaliste 22, 10000 Zagreb, Croatia – <u>www.logicbricks.com</u> Copyright © Xylon d.o.o. Xylon and logicBRICKS by Xylon are trademarks of Xylon. All other trademarks and registered trademarks are the property of their respective owners.