Size of the logi3D Scalable 3D Graphics Accelerator IP Core It is a well-known fact that a simple re-targeting of ASIC code to FPGAs cannot provide the best results in terms of programmable logic consumption and speed. Optimal results can be achieved only through an IP development that targets the programmable logic from the beginning - a careful selection of algorithms, HW/SW partitioning, coding guidelines, use of integrated blocks (BRAMs, DSPs,...), and other considerations. Xylon has designed the logi3D from the ground up for implementation in Xilinx® Zynq®-7000 All Programmable SoC!

The estimated resource utilization of the full-sized logi3D IP core

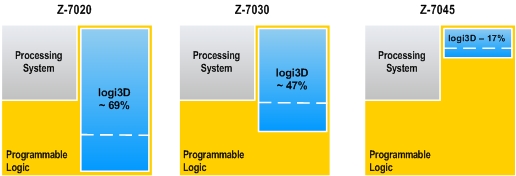

The estimated resource utilization of the full-sized logi3D IP core The figure above shows the estimated logi3D IP core's size in the Zynq-7000 AP SoC.

Users can further optimize the IP core by switching off the unneded IP core's functions. For example, the dotted line on the above figure shows its size with the second Texture Unit switched off.

The first Xylon's 3D demos do not use the second Texture Unit.

|

Performance of the logi3D Scalable 3D Graphics Accelerator IP Core

The following charts show the logi3D performance measured by logicBRICKS reference designs running Xylon 3D demo applications on Xilinx ZC702 and ZC706 Evaluation Kits. The kits run the Linux OS and OpenGL® ES 1.1 API. The logi3D Geometry Engine is implemented in software and runs on a single ARM Cortex-A9 processor on the Zynq-7000 SoC. The logi3D Rasterizer Engine runs in the Zynq-7000 programmable logic.

The Performance of the logi3D - Geometry Engine

The chart above shows that a software-based graphics acceleration (the Geometry Engine) cannot perform as well as full hardware implementations of graphics accelerators. Based on the above information, Xylon's design team has had to overcome this performance trade-off is order to enable feasible logi3D implementations in programmable logic.

The chart below shows the performance of the logi3D IP core's hardware-implemented Rasterizer Engine which compensates for the lack of the Geometry Engine's performance and significantly improves the overall graphics performance. Click

HERE to see Xylon logi3D demo!

The Estimated Performance of the logi3D - Rasterizer Engine Product is based on a published Khronos specification, and is expected to pass the Khronos Conformance Testing Process. Current conformance status can be found at www.khronos.org/conformance.

Read More:

- 3D Graphics for Xilinx AP SoC and FPGA -

About logi3D IP Core

- Use Scenarios

- Demo - Video Clip