# IogiHSSL-ZU FPGA HSSL Starter Kit

July 18<sup>th</sup>, 2024 Data Sheet Version: v2.0

# Xylon d.o.o.

Fallerovo setaliste 22 10000 Zagreb, Croatia Phone: +385 1 368 00 26 Fax: +385 1 365 51 67

E-mail: <a href="mailto:support@logicbricks.com">support@logicbricks.com</a>

URL: <a href="mailto:www.logicbricks.com">www.logicbricks.com</a>

Figure 1: logiHSSL-ZU FPGA HSSL Starter Kit

#### **Features**

- Combines the Infineon AURIX<sup>™</sup> microcontroller and the AMD Zynq<sup>™</sup> UltraScale+<sup>™</sup> adaptive SoC

- Integrates Infineon High Sped Serial Link (HSSL) optimized for AMD FPGA implementations

- Includes the complete reference design with the evaluation logicBRICKS IP cores:

- logiHSSL Slave HSSL Controller

- Linked devices can access and control each other's resources

- Complete hardware platform includes:

- 1x AMD Zynq™ UltraScale+™ MPSoC ZCU104 Evaluation Kit

- 1x Infineon Aurix Evaluation Board Kit KIT\_A2G\_TC397\_S\_TR

- 1x Xylon HSSL FMC daughter card for cable connection

- 1x FireWire cable

- Design is prepared for the AMD Vivado™ Design Suite

- Documentation and tech support (e-mail)

# **Applications**

Emerging automotive and industrial applications, such as the Advanced Driver Assistance (ADAS) and Automated Driving (AD), are both performance hungry and safety-critical.

## **General Description**

The logiHSSL-ZU FPGA HSSL Starter Kit design provides system designers with everything they need to quickly interconnect the Infineon AURIX™ microcontrollers with the AMD SoC devices via the Infineon High Speed Serial Link (HSSL). Combinations of these devices solve the rising safety and performance requirements in emerging automotive and industrial designs.

Kit deliverables include the complete reference design built around the logiHSSL Slave HSSL Controller IP core, which enables the linked devices to access and control each other's internal and connected resources. Like other Xylon logicBRICKS IP cores, the logiHSSL is prepared for the AMD Vivado™ Design Suite and come with 1-month evaluation IP license, documentation and support.

The logiHSSL IP core enables the high-speed HSSL communication between microcontrollers of Infineon's TC2xx, TC3xx and TC4xx AURIX microcontrollers family and AMD SoC (System-on-Chip) and FPGA (Field Programmable Gate Arrays). This serial link supports baudrates of up to 320 Mbaud at a net payload datarate of up to 84%.

To learn more about the logiHSSL IP core, please visit <a href="https://www.logicbricks.com/Products/logiHSSL.aspx">https://www.logicbricks.com/Products/logiHSSL.aspx</a>.

# **Design Framework**

### **Hardware Design Files**

- Configuration bitstream file for the programmable logic and the Vitis export of the reference design that allows immediate start and software changes

- ZC706, ZCU102 and ZCU104 development board reference designs prepared for the Vivado<sup>™</sup> Design Suite 2021.2

- Xylon evaluation logicBRICKS IP cores:

- logiHSSL Slave HSSL Controller

#### Software

logiHSSL application for set up and initialization of the logiHSSL IP core.

#### **Binaries**

- Precompiled SD card image for the fastest demo start-up

- First Stage Bootloader (FSBL)

- Standalone logiHSSL application example

#### **Hardware**

The logiHSSL-ZU Starter kit includes the following hardware parts:

- AMD Zynq<sup>TM</sup> UltraScale+<sup>TM</sup> MPSoC ZCU104 Evaluation Kit: https://www.xilinx.com/products/boards-and-kits/zcu104.html

- Infineon Aurix Evaluation Board Kit KIT\_A2G\_TC397\_S\_TR: https://www.infineon.com/cms/en/product/evaluation-boards/kit a2g tc397xa trb s/

- Xylon HSSL FMC daughter card

- FireWire cable used only as a physical medium

# **Reference Design**

The pre-verified reference design provides system designers with everything they need to quickly interconnect the Infineon AURIX microcontrollers with AMD programmable device. The design is created by the AMD Vivado™ Design Suite and the AMD Vitis™ 2021.2 toolsets. The reference designs demonstrates bi-directional accesses between the logiHSSL IP and the on-board system DDR memory.

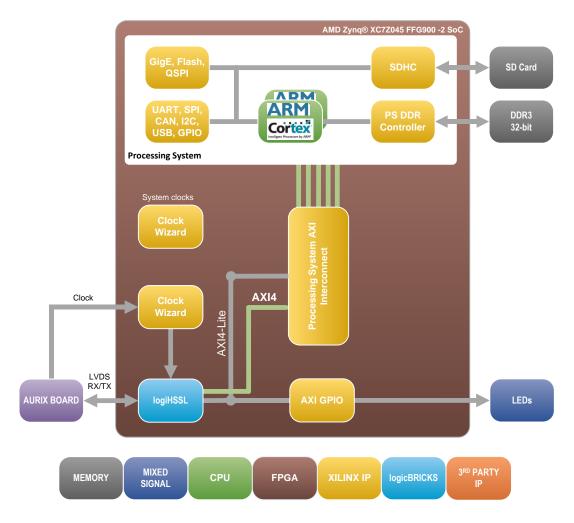

Figure 2: Reference Design Block Diagram

The logiHSSL IP core is connected to the AXI4 bus and users can modify design to enable the logiHSSL IP core accesses to other AXI4 addressable resources, such as other IP cores' register spaces, MIG controller, etc. All design clocks required for the logiHSSL IP core are generated by the AMD Clock Wizard. The HSSL reference clock is selected between external and internal clock by the mux in the Clock Wizard. The below figure shows a detail from the reference design.

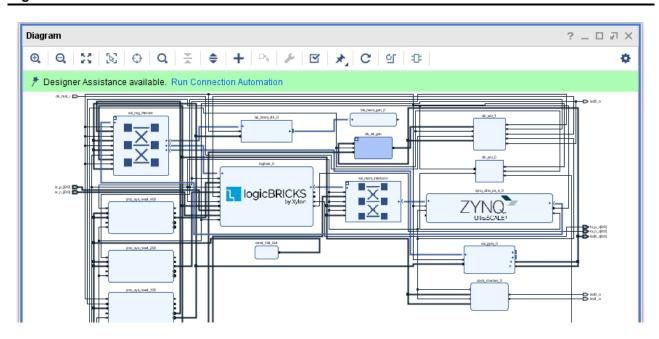

Figure 3: Implementing the logiHSSL in the Vivado Block Design

## **Available Support Products**

Xylon logiHSSL IP core enables easy interfacing between Infineon's AURIX family (TC2xx and TC3xx) and AMD SoC and FPGA devices via the Infineon High Speed Serial Link (HSSL). To learn more and get the IP core datasheet, please visit:

Email: sales@logicbricks.com

URL: https://www.logicbricks.com/Products/logiHSSL.aspx

### **Ordering Information**

This product is available directly from Xylon. Please visit our web shop or contact Xylon for pricing and additional information:

Email: sales@logicbricks.com

URL: https://www.logicbricks.com/Products/logiHSSL-ZU.aspx

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. Xylon products are not intended for use in life support applications. Use of Xylon products in such appliances is prohibited without written Xylon approval.

### **Related Information**

#### **AMD**

For information on AMD programmable logic or development system software, contact your local AMD sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124

Phone: +1 408-559-7778 URL: <u>www.amd.com</u>

### Infineon AURIX/TriBoard and HSSL

Infineon Technologies AG

AM Campeon 1 - 15

85579 Neubiberg, Germany

URL: www.infineon.com

# **Revision History**

| Version | Date        | Note                                 |

|---------|-------------|--------------------------------------|

| 1.00.   | 02.12.2019. | Initial public release.              |

| 1.01.   | 14.02.2020. | Update for release of HSSL IP v1.1.1 |

| 1.02.   | 15.03.2021. | Update for release of HSSL IP v1.2.1 |

|         | 16.11.2021. | Updated for Vivado 2021.2.           |

| 2.01.   | 18.07.2024. | Update for release of HSSL IP v2.0.1 |