# IogiREF-VIDEO-ISP-EVK

Xylon logicBRICKS<sup>™</sup> Image Signal Processing (ISP) Reference Design for Xilinx<sup>®</sup> Zynq<sup>®</sup>-7000 AP SoC based MicroZed Embedded Vison Development Kit

Version: 1.00.a

logiREF-VIDEO-ISP-EVK\_v1\_00\_a.docx

December 15<sup>th</sup>, 2014

Version: v1.00.a

Designed by XYLON

All rights reserved. This manual may not be reproduced or utilized without the prior written permission issued by Xylon.

Copyright © Xylon d.o.o. logicBRICKS<sup>™</sup> is a registered Xylon trademark.

All other trademarks and registered trademarks are the property of their respective owners.

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure to take appropriate action so that their use of our products does not infringe upon any patents.

Designed by XYLON

#### IogiREF-VIDEO-ISP-EVK ISP Reference Design User's Manual

December 15<sup>th</sup>, 2014

Version: v1.00.a

| 1 | INTRODUCTION                                                                                                                                                                            | 5                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 2 | <ul> <li>1.1 HARDWARE PLATFORM.</li> <li>1.2 DESIGN DELIVERABLES.</li> <li>1.2.1 Hardware Design Files</li></ul>                                                                        | 7<br>7<br>7<br>7<br>7<br>7<br>8<br>8<br>8<br>8 |

| 3 | <ul> <li>2.1 ABOUT LOGICBRICKS IP LIBRARY</li></ul>                                                                                                                                     | 10<br>11<br>12<br>13<br>13<br>13<br>14<br>15   |

| 4 | <ul> <li>3.1 REGISTRATION PROCESS</li></ul>                                                                                                                                             | 18<br>19<br>21                                 |

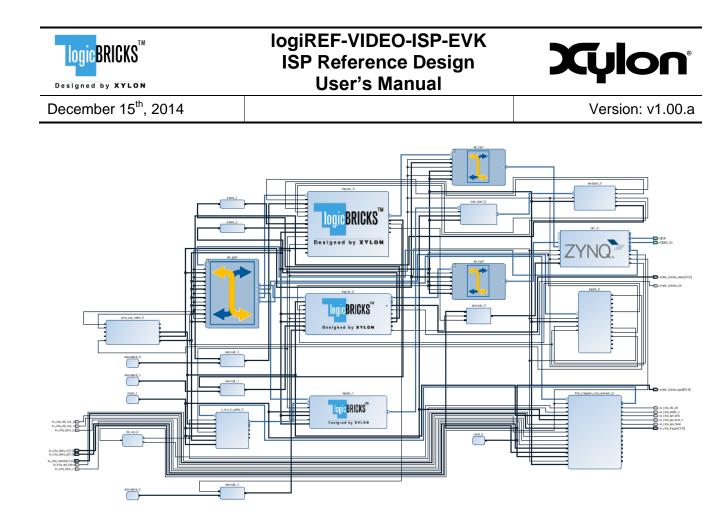

| 5 | LOGIREF-VIDEO-ISP-EVK DESIGN                                                                                                                                                            | 26                                             |

| 6 | <ul> <li>5.1 DESIGN CUSTOMIZATION</li></ul>                                                                                                                                             | 28<br>29<br>30                                 |

| 7 | <ul> <li>6.1 SET UP THE MICROZED EVK KIT FOR USE WITH THE PRECOMPILED LINUX DEMO FROM THE S</li> <li>CARD 32</li> <li>6.2 RUNNING THE PRECOMPILED DEMO FROM THE SD CARD IMAGE</li></ul> | 33                                             |

| 8 | <ul> <li>7.1 SOFTWARE INSTRUCTIONS – STANDALONE SOFTWARE</li> <li>7.2 SOFTWARE INSTRUCTIONS – LINUX SOFTWARE</li> <li>LOGIISP DEMO APPLICATION</li></ul>                                | 34                                             |

|   | <ul> <li>8.1 MAIN CONTROLS</li></ul>                                                                                                                                                    | 36<br>36<br>36                                 |

December 15<sup>th</sup>, 2014

<mark>logic</mark>BRICKS<sup>™</sup>

Version: v1.00.a

| 8.2.4 CCM – Color Correction Matrix Block | 36 |

|-------------------------------------------|----|

| 8.2.5 GAMMA – Gamma Correction Block      |    |

|                                           |    |

| 8.2.6 Enhance – Image Enhancement Block   |    |

| 8.3 BYPASS ALL AND RESET ALL BUTTONS      |    |

| 8.3.1 Bypass ALL Button                   |    |

| 8.3.2 Reset ALL Button                    |    |

| 9 REVISION HISTORY                        |    |

|                                           |    |

### **1 INTRODUCTION**

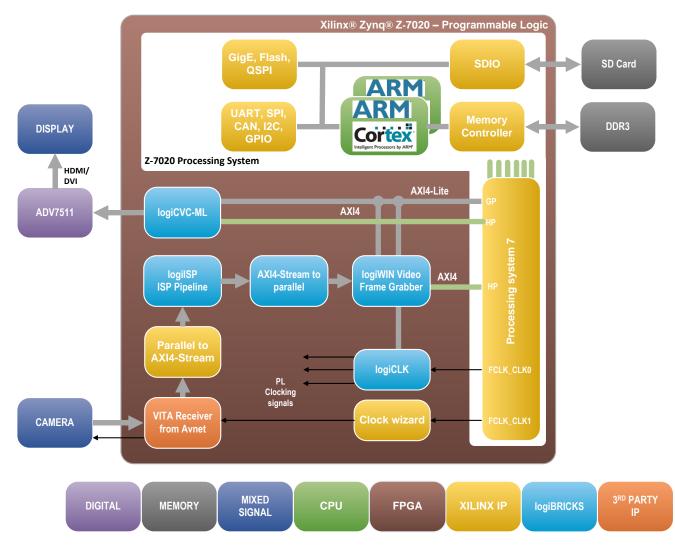

Xylon's logiISP Image Signal Processing (ISP) Pipeline IP core is a full high-definition ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx® Zynq®-7000 All Programmable SoC and 7 Series FPGA devices.

The logiISP IP core accepts diversely formatted video inputs generated by different sensors and removes defective pixels, de-mosaics Bayer encoded video, makes image color and gamma corrections, filters the noise from the video, collects video analytics data for various control algorithms and manipulates video data formats and color domains. IP core deliverables include the software driver, documentation and technical support. The IP core can be used with processor-based control algorithms for Auto White Balancing (AWB) and Auto Exposure (AE) that can be licensed from Xylon.

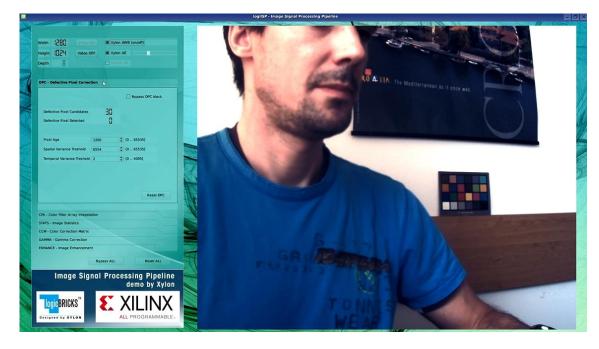

#### Figure 1 Screenshot from the Xylon Image Sensor Processing Pipeline (logiISP) Demo

Figure 2 and Figure 3 illustrate video quality enhancements achievable by the logiISP ISP pipeline IP core. Figure 3 shows the logiISP video output after the processing of the low-quality video input image shown on Figure 2.

This user's manual describes Xylon's logiREF-VIDEO-ISP-EVK ISP pipeline reference design for the MicroZed<sup>™</sup> Embedded Vision Development Kit from Avnet Electronics Marketing and the ON Semiconductor's PYTHON-1300 1.3 MP video camera. This free and pre-verified logicBRICKS reference design includes evaluation logicBRICKS IP cores and hardware design files prepared for Xilinx Vivado® Design Suite. It also includes the complete Linux OS image, software drivers, demo applications and documentation.

| LOGICBRICKS™<br>Designed by XYLON | logiREF-VIDEO-ISP-EVK<br>ISP Reference Design<br>User's Manual | Xylon            |

|-----------------------------------|----------------------------------------------------------------|------------------|

| December 15 <sup>th</sup> , 2014  |                                                                | Version: v1.00.a |

The offered evaluation hardware design is customizable. logicBRICKS IP cores can be setup through the Vivado IP Integrator (IPI) and design users can evaluate different logilSP features, make changes on the logicBRICKS graphics sub-system and add third-party IP cores required by the target application.

Figure 2: Example logiISP Video Input

#### **1.1 Hardware Platform**

The logiREF-VIDEO-ISP-EVK Image Signal Processing (ISP) Reference Design works with the the MicroZed Embedded Vision Kit from Avnet Electronics Marketing. A full evaluation requires the following hardware components:

- MicroZed Embedded Vision Development Kit (Part Number\*: AES-MBCC-EMBV-DEV-KIT) or the equivalent combination built of:

- $\circ$  MicroZed 7020 SOM

- (Part Number\*: AES-Z7MB-7Z020-SOM-G)

- MicroZed Embedded Vision Carrier Card Kit (Part Number\*: AES-MBCC-EMBV-G)

and:

ON Semiconductor PYTHON-1300-COLOR Camera (Part Number\*: AES-CAM-ON-P1300C-G)

\* Avnet Electronics Marketing part number – for more details visit www.microzed.org

Figure 4: Avnet MicroZed Embedded Vision Kit

Designed by XYLON

#### IogiREF-VIDEO-ISP-EVK ISP Reference Design User's Manual

December 15<sup>th</sup>, 2014

#### 1.2 Design Deliverables

#### 1.2.1 Hardware Design Files

- Configuration bitstream file for the programmable logic

- MicroZed Embedded Vision Kit reference design prepared for Vivado Design Suite

- Xylon evaluation logicBRICKS IP cores:

- logilSP Image Signal Processing (ISP) Pipeline

- logiWIN Versatile Video Input

- logiCVC-ML Compact Multilayer Video Controller

- logiCLK Programmable Clock Generator

- Avnet IP cores: FMC Imageon Vita Receiver

#### 1.2.2 Software

- standalone (bare metal) driver with the logiISP driver example and Linux user space driver

- standalone (bare metal) and Linux user space libraries (OSlib)

- Linux Framebuffer driver for the logiCVC-ML IP core (display controller IP core)

#### 1.2.3 Binaries

- Linux binaries containing precompiled SD Card image for the fastest demo startup:

- o logilSPDemoQt logilSP demo application with the GUI designed by the Linux Qt

- o uboot, dtb(dts), root file system

- ulmage kernel with framebuffer driver for logiCVC-ML

- qt.image compressed precompiled Qt application framework

- Standalone binaries (zynq\_fsbl, logilSP\_demo)

- FPGA bitstream

#### 1.3 Usage Modes

The logiREF-VIDEO-ISP-EVK reference design can be used in different ways, which are listed in this paragraph and thoroughly explained through this document.

#### 1.3.1 Quick Evaluation with no HW and/or SW Changes

- Download and install the logiREF-VIDEO-ISP-EVK reference design (chapter 2.5 GET AND INSTALL THE REFERENCE DESIGN)

- Setup the demo hardware and use the provided SD card image to run precompiled demo applications (paragraph 6.1 Set Up the MicroZed EVK kit for Use with the Precompiled Linux Demo From the SD Card)

December 15<sup>th</sup>, 2014

logicBRICKS<sup>™</sup>

Designed by XYLON

Version: v1.00.a

#### 1.3.2 Develop Standalone and Linux Software, no HW Changes

- Download and install the logiREF-VIDEO-ISP-EVK reference design (chapter 2.5 GET AND INSTALL THE REFERENCE DESIGN)

- Setup the demo hardware (paragraph 6.1 Set Up the MicroZed EVK kit for Use with the Precompiled Linux Demo From the SD Card)

- Use the provided Zynq-7000 AP SoC as it is (binaries)

- Follow instructions for working with logicBRICKS standalone (bare-metal) or Linux drivers (please get the full instructions in the *start.html* file from your installation root directory)

- Develop software applications prior to the availability of the actual target system

#### **1.3.3 Full ISP Customization, HW and SW Changes**

- Download and install the logiREF-VIDEO-ISP-EVK reference design (chapter 2.5 GET AND INSTALL THE REFERENCE DESIGN)

- Setup the demo hardware (paragraph 6.1 Set Up the MicroZed EVK kit for Use with the Precompiled Linux Demo From the SD Card)

- Obtain logicBRICKS evaluation licenses from Xylon (chapter 4 GETTING LOGICBRICKS EVALUATION LICENSES)

- Use the provided Zynq-7000 AP SoC to add or remove more logicBRICKS IP cores and/or third-party IP cores, or to change logicBRICKS IP settings through the GUI

- Implement new Zynq-7000 AP SoC design

- Develop software by following instructions listed in the *start.html* file from your installation root directory

#### 1.4 Xilinx Development Software

The logiREF-VIDEO-ISP-EVK reference design and Xylon logicBRICKS IP cores are fully compatible with Vivado Design Suite 2014.2. Future design releases shall be synchronized with the newest Xilinx development tools.

#### 1.5 ISP Demo Preview

Please check Xylon's Video Gallery web pages (<u>http://www.logicbricks.com/logicBRICKS-IP-Library/Video-Galleries/logicBRICKS-Demos-Xilinx-ISP-Processing.aspx</u>) to preview the Image Signal Processing (ISP) demo provided with the logiREF-VIDEO-ISP-EVK installation for your MicroZed EVK development kit.

Designed by XYLON

### 2 LOGICBRICKS IP CORES

#### 2.1 About logicBRICKS IP Library

Xylon's logicBRICKS IP core library provides IP cores optimized for Xilinx FPGAs and Zynq-7000 All Programmable SoC. logicBRICKS IP cores shorten development time and enable fast design of complex embedded systems based on Xilinx All Programmable devices. The key features of the logicBRICKS IP cores are:

- Compatibility<sup>\*</sup> with the Xilinx Vivado and ISE Design Suites logicBRICKS can be used in same ways as Xilinx IP cores and require no skills beyond general tools knowledge. IP core feature sets and programmable logic utilization can be setup through Xilinx tool GUI.

- Each logicBRICKS IP core comes with the extensive documentation, reference design examples and can be evaluated on reference hardware platforms. Xylon provides evaluation logicBRICKS IP cores to enable risk-free evaluation prior to purchase.

- Broad software support from bare-metal software drivers to standard software drivers for different operating systems (OS).

- Xylon assures skilled technical support.

| Search: Q   | T                                                                                                                                  |                                  |                         |                    |                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------|--------------------|------------------------------------------|

| Name        | *1                                                                                                                                 | AXI4                             | Status                  | License            | VLNV                                     |

| 🖃 🗁 Allian  | ce Partners                                                                                                                        |                                  |                         |                    |                                          |

| 🖻 🗁 X       | lon                                                                                                                                |                                  |                         |                    |                                          |

|             | 2D Graphics Accelerator Bit Block Transfer                                                                                         | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logibitblt:0 |

|             | Audio I2S Transmitter/Receiver                                                                                                     | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logii2s:0.0  |

|             | Bitmap 2.5D Graphics Accelerator                                                                                                   | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logibmp:0.   |

|             | I2C Bus Master Controller                                                                                                          | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logii2c:0.0  |

|             | Multilayer Video Controller                                                                                                        | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logicvc:0.0  |

|             | Perspective Transformation and Lens Correction Image Process                                                                       | or AXI4, AXI4-Stream             | Production              | Included           | logicbricks.com:logicbricks:logiview:0   |

|             | Scalable 3D Graphics Accelerator                                                                                                   | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logi3d:0.0   |

|             | SD Card Host Controller                                                                                                            | AXI4                             | Production              | Included           | logicbricks.com:logicbricks:logisdhc:0   |

| 🗄 🗁 Autor   | notive & Industrial                                                                                                                |                                  |                         |                    |                                          |

| 🗄 🗁 AXI I   | nfrastructure                                                                                                                      |                                  |                         |                    |                                          |

| 🗄 🗁 Basel   | P                                                                                                                                  |                                  |                         |                    |                                          |

| 🗄 🗁 Basic   | Elements                                                                                                                           |                                  |                         |                    |                                          |

| 🗄 🗁 Comn    | unication & Networking                                                                                                             |                                  |                         |                    |                                          |

| 🖭 🗁 Debu    | g & Verification                                                                                                                   |                                  |                         |                    |                                          |

| 🗄 🗁 Digita  | I Signal Processing                                                                                                                |                                  |                         |                    |                                          |

| 🕀 🗁 Embe    | dded Processing                                                                                                                    |                                  |                         |                    |                                          |

| 🗄 🗁 FPGA    | Features and Design                                                                                                                |                                  |                         |                    |                                          |

| 🗄 🗁 Math    | Functions                                                                                                                          |                                  |                         |                    |                                          |

| 🗄 🗁 Memo    | ries & Storage Elements                                                                                                            |                                  |                         |                    |                                          |

| 🗄 🗁 Stand   | lard Bus Interfaces                                                                                                                |                                  |                         |                    |                                          |

| 🗄 🗁 Video   | & Image Processing                                                                                                                 |                                  |                         |                    |                                          |

|             |                                                                                                                                    |                                  |                         |                    |                                          |

| Details     |                                                                                                                                    |                                  |                         |                    |                                          |

| (i) IP ava  | ailable for purchase from Alliance Partner                                                                                         |                                  |                         |                    |                                          |

|             |                                                                                                                                    |                                  |                         |                    |                                          |

| Name:       | Multilayer Video Controller                                                                                                        |                                  |                         |                    |                                          |

| Interfaces  | AXI4                                                                                                                               |                                  |                         |                    |                                          |

| Description | : The logiCVC-ML - Compact Multilayer Video Controller is a grap                                                                   | nics/video display controller op | otimized for Xilinx Zyn | q-7000 All Program | mable (AP) SoC and FPGA devices. logiCVC |

|             | provides all the necessary control signals to interface directly v                                                                 |                                  |                         |                    |                                          |

|             | configuration by VHDL code parameterization. Its functions ind                                                                     |                                  |                         |                    |                                          |

|             | for the display. Multilayer support provides alpha blending, tra<br>composite video devices and CRT displays. Additionally, Digita |                                  |                         |                    |                                          |

|             |                                                                                                                                    |                                  |                         |                    | e appropriate devices.                   |

#### Figure 5: logicBRICKS IP Cores in the Vivado IP Catalog

\* logiISP IP Core is provided in the Vivado compatible version only. Please visit our web site, or contact Xylon to learn more about the tools compatibility of the specific logicBRICKS IP core.

#### IogiREF-VIDEO-ISP-EVK ISP Reference Design User's Manual

The Figure 5 shows imported logicBRICKS IP cores into Vivado Design Suite, while the Figure 6 shows a typical logicBRICKS IP core's configuration GUI.

| Re-customize IP nage Signal Processing Pipeline                 | .(1.1)                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Documentation 📄 IP Location                                     |                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Show disabled ports                                             | IP License Type Source                                                                                                                                                                                                                                                                                                                                                                                                 |

| -yS_AXI<br>⊒ -ys_axit_video<br>-ack<br>-acken m_axit_video -y ≣ | Coefficient Matrix (Range: -8.08.0)           K11         1.0         K12         0.0         K13         0.0         K14           K21         0.0         K22         1.0         K23         0.0         K13           K31         0.0         K32         0.0         K33         1.0         Coefficient           Offsets         Red Offset         0         [-255255]         Coefficient         Coefficient |

| =areseln<br>=s_axi_ack<br>=s_axi_areseln                        | Green Offset         0         [-255255]           Blue Offset         0         [-255255]           Output Clamping and Clipping         [-255255]           Clamping Value         0         [0255]           Clipping Value         255         [0255]                                                                                                                                                              |

|                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                        |

#### Figure 6: Example of logicBRICKS IP Configuration GUI

Click on the Documentation icon in the GUI opens the User's Manual of the logicBRICKS IP core!

#### 2.2 Evaluation logicBRICKS IP Cores

Xylon offers free evaluation logicBRICKS IP cores which enable full hardware evaluation:

- Imported into the Xilinx ISE Platform Studio (XPS) and/or Vivado IP Integrator (IPI)

- IP parameterization through the tool GUI interface

- Bitstream generation

- If you need to simulate logicBRICKS IP cores, please contact Xylon

The logicBRICKS evaluation IP cores are run-time limited and cease to function after some time. Proper operation can be restored by reloading the bitstream. Besides this run-time limitation, there are no other functional differences between the evaluation and fully licensed logicBRICKS IP cores.

Evaluation logicBRICKS IP cores are distributed as parts of the Xylon reference designs: <u>http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx</u>.

Specific IP cores can be downloaded from Xylon's web shop: <u>http://www.logicbricks.com/Products/IP-Cores.aspx</u>.

logicBRICKS<sup>™</sup>

Designed by XYLON

Version: v1.00.a

### 2.3 IogicBRICKS IP Cores Used in This Design

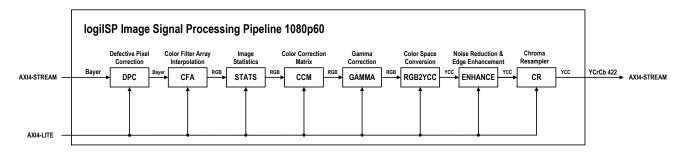

#### 2.3.1 logiISP Image Signal Processing (ISP) Pipeline

The logiISP Image Signal Processing Pipeline IP core is a full high-definition ISP pipeline designed for digital processing and image quality enhancements of an input video stream in Smarter Vision embedded designs based on Xilinx Zynq-7000 All Programmable SoC and 7 Series FPGA devices.

- Supports Xilinx Zynq-7000 AP SoC and 7 Series FPGA

- Complete and configurable ISP pipeline includes:

- Defective Pixel Correction

- Color Filter Array Interpolation

- Image Statistics (+ AWB & AE Support)

- Color Correction Matrix

- Gamma Corrections

- Image Enhancement

- Motion Adaptive Noise Reduction

- YCbCr to RGB Color-Space Converter

- RGB to YCbCr Color-Space Converter

- Chroma Resampler

- Digitally processes and enhances the quality of an input video stream and collects video statistics data for use in video control algorithms, i.e. Auto White Balance (AWB) and Auto Exposure (AE)

- Supports up to 1080p60 (1920x1080@60fps) and up to 7680x7680 at lower refresh rates

- Supports video input formats: Raw Bayer, RGB and YCbCr; color depth 8/10/12-bit

- Video input and output are ARM AMBA AXI4-Stream protocol compliant

- Optional registers are AMBA AXI4-Lite protocol compliant

- Parametrical VHDL design that allows tuning of slice consumption and features set

- Prepackaged for Xilinx Vivado Design Suite and fully controllable through the IP Integrator GUI interface

- Evaluation IP core available online and the bit-accurate C model for evaluations available on request

- IP deliverables include the software driver, documentation and technical support

- Available fee-based license extension for the AWB&AE libraries, which are verified with the logilSP IP core

More info: <u>http://www.logicbricks.com/Products/logiISP.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiISP\_hds.pdf</u>

December 15<sup>th</sup>, 2014

Version: v1.00.a

#### 2.3.2 logiCVC-ML Compact Multilayer Video Controller

The logiCVC-ML IP core is an advanced display graphics controller for LCD and CRT displays, which enables an easy video and graphics integration into embedded systems with Xilinx Zynq-7000 All Programmable SoC and FPGAs.

This IP core is the cornerstone of all 2D and 3D GPUs. Though its main function is to provide flexible display control, it also includes hardware acceleration functions: three types of alpha blending, panning, buffering of multiple frames, etc.

- Supports all Xilinx FPGA families

- Supports LCD and CRT displays (easily tailored for special display types)

- 64x1 to 2048x2048 display resolutions

- Available SW drivers for: Linux, Android, QNX and Microsoft Windows Embedded Compact OS

- Support for higher display resolutions available on request

- Supports up to 5 layers; the last one configurable as a background layer

- Configurable layers' size, position and offset

- Alpha blending and Color keyed transparency

- Pixel, layer, or Color Lookup Table (CLUT) alpha blending mode can be independently set for each layer

- Packed pixel layer memory organization:

- RGB 8-bpp, 8-bpp using CLUT, 16bpp Hi-color RGB 565 and True-color 24bpp

- YCbCr 16bpp (4:2:2) and 24bpp (4:4:4)

- Configurable CoreConnect<sup>™</sup> PLBv4.6, Xylon XMB or ARM<sup>®</sup> AMBA<sup>®</sup> AXI4 memory interface data width (32, 64 or 128)

- Programmable layer memory base address and stride

- Simple programming due to small number of control registers

- Support for multiple output formats:

- Parallel display data bus (RGB): 12x2-bit, 15-bit, 16-bit, 18-bit or 24-bit

- YCbCr 4:4:4 or 4:2:2 output format

- Digital Video ITU-656: PAL and NTSC

- LVDS output format: 3 or 4 data pairs plus clock

- Camera link output format: 4 data pairs plus clock

- DVI output format

- Supports synchronization to external parallel input

- Versatile and programmable sync signals timing

- Double/triple buffering enables flicker-free reproduction

- Display power-on sequencing control signals

- Parametrical VHDL design that allows tuning of slice consumption and features set

- Available for Xilinx Vivado IP Integrator and ISE XPS implementation tools

More info: <u>http://www.logicbricks.com/Products/logiCVC-ML.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiCVC-ML\_hds.pdf</u>

December 15<sup>th</sup>, 2014

Version: v1.00.a

#### 2.3.3 logiWIN Versatile Video Input

The logiWIN IP core enables easy implementation of video frame grabbers. Input video can be decoded, real-time scaled, de-interlaced, cropped, antialiased, positioned on the screen...

- Supports Xilinx Zynq-7000 AP SoC and FPGAs

- Maximum input and output resolutions 2048x2048

- Supports different input interface standards: ITU656 and ITU1120 (PAL and NTSC), RGB, YUV 4:2:2

- Built-in YCrCb to RGB, YUV to RGB and RGB to YCrCb converters

- Real-time scale-up to 64x and scale-down to 16x; lossless scaling down to 2x or 4x in the cascade scaling mode

- Supports video de-interlacing, cropping, positioning, pixel alpha blending...

- Embedded image color enhancements: brightness, contrast, hue, saturation

- ARM AMBA AXI4 and AXI4-Lite bus compliant

- Available for Xilinx Vivado IP Integrator and ISE XPS implementation tools

More info: <u>http://www.logicbricks.com/Products/logiWIN.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiWIN\_hds.pdf</u>

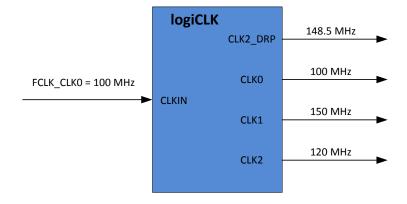

#### 2.3.4 logiCLK Programmable Clock Generator

The logiCLK is a programmable clock generator IP core featuring twelve independent and fully configurable clock outputs. While six clock outputs can be fixed by generic parameters prior to the implementation, the other six clock outputs can be either fixed by generics or dynamically reconfigured in a working device.

- Supports Xilinx Zynq-7000 All Programmable SoC, 7 series and Spartan<sup>®</sup>-6 FPGAs

- Provides 12 independent clock outputs that can be configured by generic parameters:

- 6 outputs can be dynamically configured through the DRP interface

- 6 outputs can be configured by generics only

- Input clock frequency range\*:

- Spartan-6: 19 540 MHz

- 7 series: 19 1066 MHz

- Output clocks frequency range\*:

- Spartan-6: 3.125 400 MHz

- 7 series: 6.25 741 MHz

- Configurable ARM AMBA AXI4-Lite and CoreConnect PLBv46 compliant registers interface

- Software support for Linux and Microsoft Windows Embedded Compact operating systems

- Available for Xilinx Vivado IP Integrator and ISE Platform Studio

- \* Depending on the used device's speed grade

More info: <u>http://www.logicbricks.com/Products/logiCLK.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiCLK\_hds.pdf</u>

Version: v1.00.a

#### 2.4 logicBRICKS IP Cores for Graphical User Interface (GUI) Implementations

Xylon's logicBRICKS library of IP cores optimized for Xilinx All Programmable devices includes several graphics logicBRICKS IP cores for full range implementation of 2D and 3D Graphics Processing Units (GPU) on Xilinx Zynq-7000 All Programmable SoC and FPGAs.

Xylon's graphics logicBRICKS IP cores can be quickly combined with the video processing IP cores when it is necessary to support complex GUI interfaces. Graphics logicBRICKS IP cores are well supported by Xylon provided software drivers for the most popular operating systems: Linux, Android<sup>™</sup>, QNX<sup>®</sup> and Microsoft<sup>®</sup> Windows<sup>®</sup> Embedded Compact. A number of Xilinx partners who provide BSPs (Board Support Package) for different operating systems support Xylon logicBRICKS IP cores for graphics.

#### Figure 7: Screenshots from Some Demos Provided with the Reference Designs (logiREF-ZGPU-ZED, logiREF-ZGPU-ZC702 and logiREF-ZGPU-ZC706)

To get Xylon free GUI reference designs, please visit:

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx

To learn more about the available software support for graphics logicBRICKS IP cores, please visit:

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/OS-IP-Core-Support.aspx

#### logiBITBLT Bit Block Transfer 2D Graphics Accelerator

This 2D graphics accelerator speeds up the most common GUI operations and offloads the processor. The logiBITBLT transfers graphics objects from one to another part of system's on-screen or off-screen video memory, and performs different operations during transfers, such as ROP2 raster operations, bitmap scaling (stretching) and flipping, Porter & Duff compositing rules or transparency.

More info: <u>http://www.logicbricks.com/Products/logiBITBLT.aspx</u> Datasheet: <u>http://www.logicbricks.com/Documentation/Datasheets/IP/logiBITBLT\_hds.pdf</u>

#### logi3D Scalable 3D Graphic Accelerator

The logi3D\* Scalable 3D Graphics Accelerator IP core is a 3D Graphics Processing Unit (GPU) IP core developed for embedded systems based on the Xilinx Zynq-7000 All Programmable SoC. The IP is designed to support the OpenGL ES 1.1 API specifications – a royalty-free, cross-platform API for full-function 2D and 3D graphics on embedded systems – including consoles, phones, appliances and vehicles.

\* Product is based on a published Khronos specification, and is expected to pass the Khronos Conformance Testing Process. Current conformance status can be found at <u>www.khronos.org/conformance</u>.

#### 2.5 Complementary logicBRICKS Reference Design – Face Tracking

The face detection and tracking is a computer technology that uses video images captured by the video camera to determine and track distinctive facial features. The technology significantly improves human-machine interaction and opens a very wide range of applications, such as adriver drowsiness detection in automotive safety systems that prevent accidents, speaker detection in video conferencing systems capable to automatically zoom to the current speaker, hands-free interfacing helping disabled people to improve their daily lives, character animations in virtual reality entertainment and gaming, health, robotics, audio processing and others.

To learn more about this technology and to evaluate Xylon's solution designed for Xilinx All Programmable, please check Xylon's free downloadable logiREF-FACE-TRACK-EVK Face Detection and Tracking reference design for the MicroZed<sup>™</sup> Embedded Vision Development Kit from Avnet Electronics Marketing and the ON Semiconductor's PYTHON-1300 1.3 MP video camera:

<section-header>

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/Face-Detection-for-Zyng-AP-SoC.aspx

Figure 8: Screenshot from the Xylon Face Tracking Demo

Designed by XYLON

December 15<sup>th</sup>, 2014

Version: v1.00.a

### **3 GET AND INSTALL THE REFERENCE DESIGN**

Xylon offers several logicBRICKS reference designs for different hardware platforms. Short descriptions of all Xylon logicBRICKS reference designs can be found at:

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx

A quick access to specific reference design is also possible through the main downloads navigation page: <u>http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/Xylon-Reference-Designs-Navigation-Page.aspx</u>

Only registered logicBRICKS users can download logicBRICKS reference designs. Unregistered users will be re-directed to the User Login page. The download link is automatically sent by an e-mail, which means that the registration process requires access to the e-mail account. Xylon reference logicBRICKS designs can be downloaded as cross-platform Java JAR self-extracting installers.

For quick registration and other general instructions, please visit:

http://www.logicbricks.com/logicBRICKS/logicBRICKS-Quick-Info.aspx

#### 3.1 Registration Process

Registration is very quick and simple. If you experience any troubles during the registration process, please contact Xylon Technical Support Service – <u>support@logicbricks.com</u>.

December 15<sup>th</sup>, 2014

Login

logic<mark>BRICKS</mark>™

Designed by XYLON

<mark>llogic</mark>BRICKS<sup>™</sup>

#### Step 1

If you are the registered logicBRICKS user, please type-in your Username and Password. Unregistered users should click on the Register button, which will open the registration form.

#### Step 2

Unregistered users should fill-in the registration form from the Fig 10. Please take care on required form's fields. Your Username is an actual e-mail account used for communication with Xylon logicBRICKS. Xylon accepts only valid company e-mail accounts.

#### Step 3

As soon as your registration form gets accepted by Xylon, you get a confirmation message. Please check your e-mail to find a link that activates your logicBRICKS account. If you do not get the confirmation message in several minutes, please check your Spam Filter or Junk Mail Folder. If you have not received the confirmation message, please contact Xylon support.

### Figure 10: Registration Process – Step 2

Your e-mail will be used as login for ou web alter

#### Figure 11: Registration Process – Step 3

Version: v1.00.a

December 15<sup>th</sup>, 2014

logic<mark>BRICKS</mark>™

Designed by XYLON

logic<mark>BRICKS</mark>"

Figure 12: Registration Process – Step 4

Step 4

Step 5

As soon as you select an appropriate logicBRICKS reference design and installer for your operating system from the Downloads Navigation Page (link bellow), you will get an e-mail with the download link for the selected reference design installation.

Click on the logicBRICKS web account activation link in the received e-mail, and you will get the confirmation status message.

Please login to proceed.

http://www.logicbricks.com/logicBRICKS/Ref erence-logicBRICKS-Design/Xylon-Reference-Designs-Navigation-Page.aspx

Figure 13: Registration Process – Step 5

#### 3.2 Installation Process

Generate Download Link

Installation process is quick and easy. Each logicBRICKS reference design can be downloaded as a cross-platform Java JAR self-extracting installer. Please make sure that you have a copy of the JRE (Java Runtime Environment) version 6 or higher on your system to run Java applications and applets.

Double-click on the installer's icon to run the self-installing executable to unpack and install the reference design on your PC.

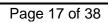

At the beginning, you will be requested to accept two evaluation licenses - Figure 14 and Figure 15.

For installation in Linux OS, please follow instructions:

http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design/Xylon-Reference-Designs-Linux-Installation.aspx.

Version: v1.00.a

| LOGIC BRICKS                     | logiREF-VIDEO-ISP-EVK<br>ISP Reference Design<br>User's Manual | Xylon            |

|----------------------------------|----------------------------------------------------------------|------------------|

| December 15 <sup>th</sup> , 2014 |                                                                | Version: v1.00.a |

If you agree with the conditions from the evaluation licenses, click NEXT and select the installation path for your logicBRICKS reference design – Figure 16.

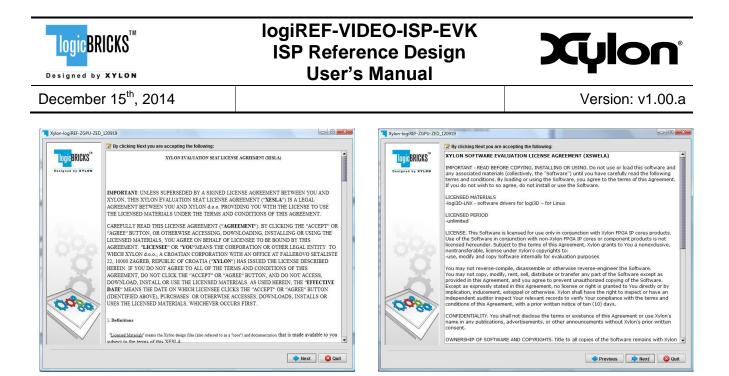

The installation process takes several minutes. It generates the directory structure described in the paragraph 3.3 Directory Structure.

#### 3.2.1 Filesystem permissions of the installed directory (Windows 7)

The reference design installed in the default path C:\Program Files\xylon will inherit read-only filesystem permissions from the parent directory. This will block you in opening the hardware project file in Xilinx Vivado tools. Therefore it is necessary to change the filesystem permissions for the current user to "Full control" preferably.

To change the user permissions for C:\Program Files\xylon directory and all of it's subdirectories, right click on the C:\Program Files\xylon directory and select "Properties". Under "Security" tab select "Edit". Select "Users" group in the list and check "Full control" checkbox in the "Allow" column.

#### Figure 14: Installation Process – Step 1

| LogicBRICKS |                                                                          |                          |

|-------------|--------------------------------------------------------------------------|--------------------------|

| 20.         | Select the installation path:<br>Dr.Program Files/ing/on/2CPU_ZED_120919 | 🔓 Browse                 |

|             | [2.erogian Frieshjonkser-220] (20919                                     | Diowse                   |

|             |                                                                          | 🗬 Previous 🔹 Next 🔇 Cuit |

#### Figure 16: Installation Process – Step 3

Figure 18: Installation Process – Step 5

#### Figure 15: Installation Process – Step 2

| 5:  |  |

|-----|--|

| 2/6 |  |

|     |  |

|     |  |

|     |  |

|     |  |

|     |  |

|     |  |

|     |  |

#### Figure 17: Installation Process – Step 4

| <mark>logic</mark> BRICKS <sup>™</sup> |

|----------------------------------------|

| Designed by XYLON                      |

Version: v1.00.a

#### 3.3 Directory Structure

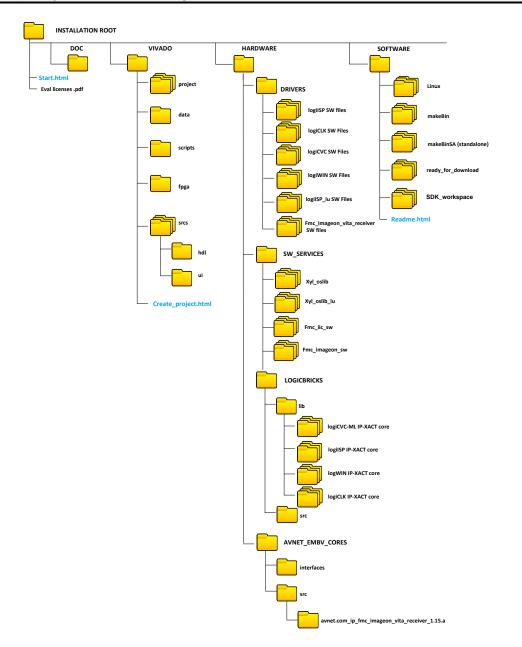

Figure 19 gives a top level view of the directories and files included with the logiREF-VIDEO-ISP-EVK reference design for the MicroZed Embedded Vision development kit. Table 1 explains the purpose of directories.

Please use the start.html file located in the installation root directory as a jump-start navigation page for exploring the reference design.

#### Figure 19: Installed Reference Design – The Directory Structure

December 15<sup>th</sup>, 2014

Version: v1.00.a

|              | Directory           | Purpose                                                    |

|--------------|---------------------|------------------------------------------------------------|

| Installation | n Root              | This directory contains the start.html page - the jump-    |

|              |                     | start navigation page through the reference design.        |

| Doc          |                     | Project documentation (Users Manual).                      |

| Vivado       |                     | This directory contains the complete Vivado project and    |

|              |                     | files necessary for regenerating project from TCL scripts. |

|              | Data                | Design constraints files.                                  |

|              | hp433ab             | Vivado project directories – recreated with TCL scripts.   |

|              | Srcs                | Block design GUI script and HDL wrappers.                  |

|              | Scripts             | TCL scripts to create block design from scratch.           |

|              | fpga                | MicroZed reference design bitstream.                       |

|              | create_project.html | Instructions for building Vivado project from scratch.     |

| Hardware     |                     |                                                            |

|              | Drivers             | Standalone (bare-metal and linux userspace) drivers for    |

|              |                     | logicBRICKS IP cores with documentation and examples       |

|              |                     | and Avnet's standalone driver for Vita Receiver.           |

|              | logicbricks/lib     | Evaluation logicBRICKS IP-XACT cores (zip archives).       |

|              | logicbricks/src     | Evaluation logicBRICKS IP-XACT extracted IP cores. IP      |

|              |                     | cores' User's Manuals are stored in doc subdirectories.    |

|              | Logicbricks/if      | logicBRICKS IPs' interface definitions for Vivado.         |

|              | avnet_embv_cores    | Avnet provided IP cores.                                   |

|              | sw_services         | xyl_oslib Xylon OS abstraction library for Linux           |

|              |                     | applications and Avnet IIC libraries.                      |

| Software     |                     |                                                            |

|              | readme.html         | Navigation page through the software files and             |

|              |                     | instructions for building binaries.                        |

|              | Linux/kernel        | Linux kernel and device tree configuration files.          |

|              | Linux/libraries     | Scripts and patches for building Qt                        |

|              | makeBin             | Utility script for creating boot.bin file (for Linux)      |

|              | makeBinSA           | Utility script for creating boot.bin file (for StandAlone) |

|              | ready_for_download  | Prepared SD binaries ready for download.                   |

|              | SDK_workspace       | Xilinx SDK workspace folder for building of bare-metal     |

|              |                     | logiISP application and linux userspace logiISP driver.    |

#### Table 1: Explanation of Directories in logiREF-VIDEO-ISP-EVK Reference Design

Designed by XYLON

#### IogiREF-VIDEO-ISP-EVK ISP Reference Design User's Manual

December 15<sup>th</sup>, 2014

Version: v1.00.a

### 4 GETTING LOGICBRICKS EVALUATION LICENSES

Please note that the logiREF-VIDEO-ISP-EVK reference design installation provides you with everything needed to run the provided demo applications or to use/change the provided software source code. However, if you wish to make any changes on the hardware design files, such as to remove, add or reconfigure some of the provided IP cores, you have to obtain evaluation IP licenses from Xylon.

The following pages describe the procedure for getting and licensing evaluation logicBRICKS IP cores that takes several minutes to complete. If you experience any troubles during this process, please contact Xylon Technical Support Service – <u>support@logicbricks.com</u>.

You must be logged in to the Xylon website using your logicBRICKS user name and password to get an access to evaluation logicBRICKS IP cores. Unregistered users will be re-directed to the User Login page. Paragraph 3.1 Registration Process explains this simple registration procedure.

**Step 1** – Logged in users get the "My logicBRICKS" tab in the main <u>www.logicbricks.com</u> navigation menu. Click on it, and you will be directed to your main web page for communication with Xylon logicBRICKS – Figure 20. Please select the "**Request Eval IP Core**" tab in the left menu.

#### Figure 20: Step 1 – My logicBRICKS Navigation Page

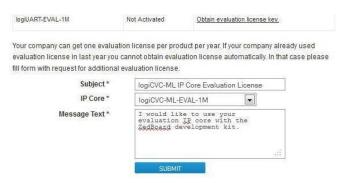

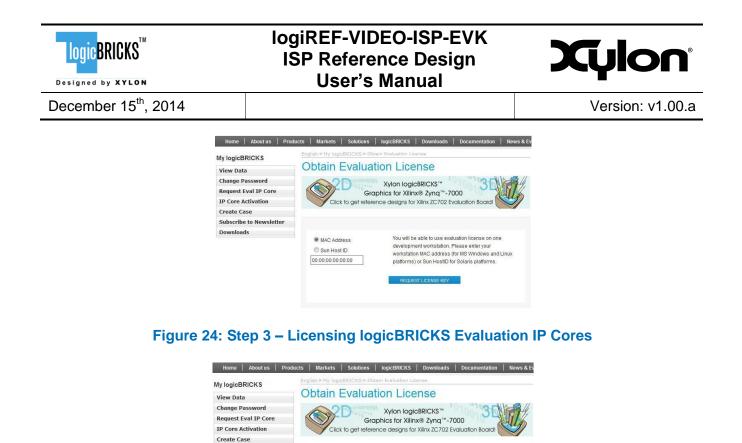

**Step 2** – Select the evaluation logicBRICKS IP core and click on "**Obtain evaluation license key**" link – Figure 21. If you are entitled to get the evaluation logicBRICKS IP core, you will be immediately asked (Figure 24) your Ethernet MAC ID number or Sun Host ID – as described in the Step 3.

If the evaluation logicBRICKS IP cores' list looks differently from the one shown on Figure 21, for example as the list presented by the Figure 22, please fill in and submit the request form (Figure 23), and allow us some time to process your request. Scroll down to get to the request form.

For instructions how to find your Ethernet MAC or host ID, please visit: <u>http://www.logicbricks.com/Documentation/Article.aspx?articleID=KBA-01186-M0JXKD</u>

December 15<sup>th</sup>, 2014

#### Version: v1.00.a

| Home   About us   Pr    | oducts   Markets    | Solutions     | logicBRICKS     | Downloads        | Documentation         | News & E |

|-------------------------|---------------------|---------------|-----------------|------------------|-----------------------|----------|

| My logicBRICKS          | English > My logicf |               |                 |                  |                       |          |

| View Data               | Evaluation          | on Lice       | ense            |                  |                       |          |

| Change Password         | A21                 | 0101001010    | Xylon logic     | BRICKS           | 100102-01             | 1034     |

| Request Eval IP Core    |                     | Gra           | phics for Xilin |                  | 000                   |          |

| IP Core Activation      | Click               | to get refere | nce designs for | Xilinx ZC702 Ev  | valuation Board! 🜔    | S.       |

| Create Case             |                     |               | Click           | to get the IP li | cense key!            |          |

| Subscribe to Newsletter | Nam                 | e             | Status          | -                | ×                     |          |

| Downloads               |                     |               | Street West     | -                |                       |          |

|                         | logiCVC-ML-EVAL-1   | M             | Not Activated   | Obtain eva       | aluation license key. |          |

|                         | logiWIN-EVAL-1M     |               | Not Activated   | Obtain eva       | aluation license key. |          |

|                         | logiBITBLT-EVAL-1M  |               | Not Activated   | Obtain eva       | aluation license key. |          |

#### Figure 21: Step 2 – Selecting logicBRICKS IP Core for Licensing

#### Figure 22: Step 2 – A List of Already Activated logicBRICKS IP Licenses

#### Figure 23: Step 1 – Licensing logicBRICKS Evaluation IP Cores

**Step 3** – Evaluation logicBRICKS IP licenses are tied to your Ethernet MAC address or Sun Host ID (Figure 24), and can be used on a single working station only. Fill in this address and click on the "**Request License Key**" button. You should get the confirmation message – Figure 25. If you do not get the confirmation message, please contact Xylon technical support – <u>support@logicbricks.com</u>.

#### Figure 25: Step 3 – Confirmation Message

License key will be created and send to your e-mail address.

Subscribe to Newsletter Downloads

**Step 4** – You will get an e-mail with the license key (file) and full instructions for setting up the license key and downloading the logicBRICKS IP core. Please follow the provided instructions.

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       | Sent:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6.9.2012 17:47                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| ct: Xvlon Core License Delivery - ID:03                                                                                                                                                                                             | 512090617423596                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| hments: 🗐 03512090617423596 ip xa                                                                                                                                                                                                   |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

| hments: 0351209061/423596_p_xa                                                                                                                                                                                                      | p_349logicvcmi_evai_flexim.lic (568 B)                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

|                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4. mar.                                 |

| logic BRICKS <sup>™</sup>                                                                                                                                                                                                           | ** THIS IS AN AUTOMATICALLY                                                                                                                                                                                           | GENERATED EMAIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | **                                      |