# **logiSDHC Secure Digital Host Controller**

**Core Facts**

October 2<sup>nd</sup>, 2019 Data Sheet Version: v2.2

## Xylon d.o.o.

Fallerovo setaliste 22 10000 Zagreb, Croatia Phone: +385 1 368 00 26

Fax: +385 1 365 51 67

E-mail: support@logicbricks.com

Www.logicbricks.com

# **Features**

- Supports Xilinx<sup>®</sup> 7 Series, including Spartan 7 and Zyng<sup>®</sup>-7000 All Programmable SoC

- Supports Xilinx<sup>®</sup> Ultrascale<sup>™</sup>, Ultrascale+<sup>™</sup> and Zynq<sup>®</sup> UltraScale<sup>™</sup>, Zynq<sup>®</sup> UltraScale+<sup>™</sup> MPSoCs

- Plug-and-Play Standard and High Capacity SD cards to Xilinx All Programmable devices

- Secure Digital Host Controller compliant with Secure Digital Specifications Version 2.00

- · Evaluation IP core available online

- Available software drivers enable easy use with Linux OS and without the OS (bare-metal)

- **Provided with Core** Documentation User's Manual Design File Formats **Encrypted VHDL** Constraints Files Please contact Xylon Reference Designs & Please contact Xylon **Application Notes** Additional Items FatFs - Generic FAT File System Module Linux OS software driver OS-independent IP SW driver Simulation Tool Used ModelTech's Modelsim Support Support provided by Xylon

- Programmable transfer rates up to the maximum data rate specified by the standard (25 MB/sec and 50 MHz bus frequency)

- Supports non-DMA and standard DMA data transfers

- The standard DMA supports enhanced features:

- Read/write memory burst cycles (16, 32 or 64 clock cycles)

- Interrupted memory burst cycles

- Byte address boundary memory accesses

- DMA interrupt mechanism compliant to the supported SD standard

Table 1: Example Implementation Statistics for Xilinx® FPGAs

| Family                                                                        | Fmax (MHz) |                          |      | 1                | 1               | 2.4                |      | MULT/   | Design           |

|-------------------------------------------------------------------------------|------------|--------------------------|------|------------------|-----------------|--------------------|------|---------|------------------|

| (Device)                                                                      | mclk       | sd_base_clk <sup>3</sup> | rclk | LUT <sup>1</sup> | FF <sup>1</sup> | IOB <sup>2,4</sup> | BRAM | DSP48/E | Tools            |

| Zynq <sup>®</sup> -7000<br>(xc7z020clg484-1)                                  | 100        | 100                      | 100  | 1329             | 1215            | 6                  | 2    | 1       | Vivado<br>2018.3 |

| Kintex®-7<br>(XC7K325T-2)                                                     | 100        | 100                      | 100  | 1370             | 1219            | 6                  | 2    | 1       | Vivado<br>2018.2 |

| Zynq <sup>®</sup> UltraScale+ <sup>TM</sup><br>(xczu9eg-ffvb1156-1-i-<br>es1) | 100        | 100                      | 100  | 1317             | 1214            | 6                  | 2    | 1       | Vivado<br>2018.3 |

#### Notes:

<sup>1)</sup> Assuming the following configuration: AXI4-Lite registers interface, 32-bit AXI4 memory interface for standard DMA and 32 clock cycles burst.

<sup>2)</sup> Assuming only SD Card interface signals are routed off-chip, auxiliary signals, register and memory interface are connected internally.

<sup>3)</sup> Maximum sd\_base\_clk frequency according to Secure Digital Specification Version 2.00 is 100 MHz.

<sup>4)</sup> SD card write protect, card detect and LED indicator ports are used off-chip, but they are not mandatory

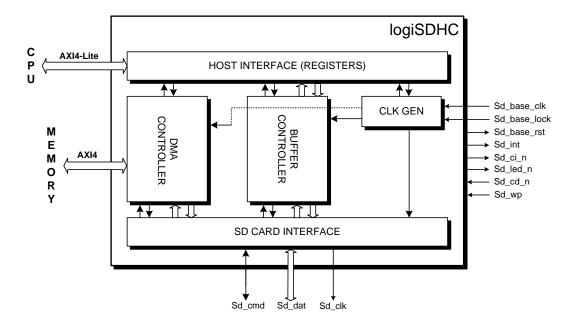

Figure 1: logiSDHC block schematic

# Features (cont)

- DMA engine supports Little and Big Endian host systems

- ARM® AMBA® AXI4-Lite register interface (32 bits)

- DMA memory interface (32 bits) designed for ARM AMBA AXI4 interface

- Buffer overflow detection of too fast read transfers which cannot be handled by the host

- Read wait stalls too fast read transfers and prevents buffer overflows on the host's side

- Parametrizable VHDL design that allows tuning of slice consumption and features set through the GUI

- Xilinx Vivado<sup>®</sup> IP Integrator compatible IP version supports the 7 Series and Zynq-7000 All Programmable SoCs, Ultrascale<sup>TM</sup>, Ultrascale+<sup>TM</sup> and Zynq<sup>®</sup> UltraScale+<sup>TM</sup> MPSoCs

- Xilinx ISE<sup>®</sup> Platform Studio compatible IP version supports older Xilinx FPGA families (contact Xylon)

- Simple Plug'n'Play with other Xylon logicBRICKS, Xilinx and third-party IP cores

- Deliverables include Generic FAT File System Module FatFs (http://elm-chan.org/fsw/ff/00index\_e.html)

### **Applications**

Electronic devices serving different vertical markets and requiring big and fast non-volatile storage:

- Consumer

- Automotive

- Industrial

- Medical

- Military, etc.

### **General Description**

The logiSDHC is the Secure Digital (SD) card Host Controller IP core from the Xylon's logicBRICKS IP core library optimized for Xilinx All Programmable devices. It is designed to transfer data from the system memory to the SD card's data bus, and vice versa. The IP core enables expansion of Xilinx FPGA and SoC devices based embedded systems by mass storage capabilities. The available software drivers enables its extremely simple use under the Linux operating system, or in embedded systems without the operating systems (bare-metal).

The logiSDHC IP core is the SD Host Controller Standard Specification Version 2.00 compliant. The IP is a memory IO mapped hardware module providing a general-purpose interface between the embedded SW application and the SD card memory component.

The logiSDHC IP core supports non-DMA and DMA data transfers. Implemented DMA mechanism is compliant to the SD Host Controller Standard Specification and enables fast data transfers with minimal CPU activities. The DMA is an optional feature and can be switched off to preserve available FPGA resources.

To purchase the IP, or to download the evaluation logiSDHC IP core, please visit:

http://www.logicbricks.com/Products/logiSDHC.aspx.

## **Functional Description**

The Figure 1 presents internal logiSDHC architecture. The logiSDHC functional blocks are: Host Interface, Clock Gen, Buffer Controller, DMA Controller, SD Card Interface.

### **Host Interface**

Implements register interface according to the SD Specification Version 2.00. The host interface controls the functionality of the logiSDHC IP core through a set of control and command signals.

#### Clock Gen

Generates clock and clock enable signals for IP's sub modules and for the SD Card.

### **Buffer Controller**

Manages non-DMA data transfers.

#### **DMA Controller**

The DMA enables fast transfers to/from the system memory and the SD card. Bursts of data are buffered in Read and Write buffers that regulate data formatting and transfers between different clock domains.

### **SD Card Interface**

The card interface implements separated state machines. One state machine responses to system commands and handles SD card's responses, while the other one handles data transfers to/from the memory card.

## **Core Modifications**

The core is supplied in an encrypted VHDL format which allows the user to take full control over configuration parameters. Various logiSDHC configuration parameters are selectable prior to VHDL synthesis and can be setup through Xilinx implementation tools GUI. The following table (Table 2) presents some configuration parameters selected from a list of the available parameters:

Table 2: logiSDHC VHDL configuration parameters

| Parameter        | Description                                     |

|------------------|-------------------------------------------------|

| C USE DMA        | 0 – DMA controller not implemented              |

|                  | 1 – SD card 2.0 spec DMA controller implemented |

| C_MEM_INTERFACE  | Only AXI4 memory interface supported for Vivado |

| C_REGS_INTERFACE | Only AXI4-Lite interface supported for Vivado   |

For the complete list of parameters, please consult the logiSDHC User's Manual delivered with the IP core.

The logiSDHC is designed with regard to SD Specification Version 2.00. However, there may be instances where source code modification is necessary. Therefore, if you wish to reach the optimal use of the logiSDHC

core or to supplement some of your specific functions, you can allow us to tailor the logiSDHC to your requirements. The logiSDHC source code (VHDL sources) is available at additional cost from Xylon.

# **Core I/O Signals**

The core signal I/Os have not been fixed to specific device pins to provide flexibility for interfacing with user logic. Descriptions of all signal I/Os are provided in Table 3.

Table 3: Core I/O Signals

| Signal              | Signal<br>Direction | Description                                        |  |  |

|---------------------|---------------------|----------------------------------------------------|--|--|

| Memory Interface    |                     |                                                    |  |  |

| AXI4 Interface      | Bus                 | Refer to AMBA AXI version 4 specification from ARM |  |  |

| Register Interface  |                     |                                                    |  |  |

| AXI4-Lite Interface | Bus                 | Refer to AMBA AXI version 4 specification from ARM |  |  |

| SD Card ports       |                     |                                                    |  |  |

| SD_CLK              | Output              | SD Card clock                                      |  |  |

| SD_DAT              | Input/Output        | SD Card data                                       |  |  |

| SD_CMD              | Input/Output        | SD Card command                                    |  |  |

| Auxiliary signals   |                     |                                                    |  |  |

| SD_BASE_RST         | Output              | SD base clock DCM reset                            |  |  |

| SD_BASE_LOCK        | Input               | SD base clock DCM lock                             |  |  |

| SD_BASE_CLK         | Input               | SD base clock                                      |  |  |

| SD_INT              | Output              | SD interrupt                                       |  |  |

| SD_WP               | Input               | SD write protect switch                            |  |  |

| SD_CD_N             | Input               | SD card not present                                |  |  |

| SD_CI_N             | Output              | SD card not inserted                               |  |  |

| SD_LED_N            | Output              | LED indicating that SD Card is in use              |  |  |

### **Verification Methods**

The logiSDHC is fully supported by the Xilinx Vivado Design Suite. This tight integration tremendously shortens IP integration and verification. A full logiSDHC implementation does not require any particular skills beyond general Xilinx tools knowledge. The encrypted IP supports running simulations in Mentor Graphics ModelSim and QuestaSim, and Aldec Active HDL.

The logiSDHC evaluation IP core can be downloaded from Xylon web site and be fully evaluated in hardware: http://www.logicbricks.com/Products/logiSDHC.aspx

If you are interested in using the logiSDHC IP core with the Xilinx ISE® Design Suite and older FPGA families, please contact Xylon at <a href="mailto:info@logicbricks.com">info@logicbricks.com</a>.

# **Recommended Design Experience**

The user should have experience in the following areas:

- Xilinx design tools

- ModelSim

## **Available Support Products**

Xylon provides several free pre-verified video and graphics reference designs for the most popular Xilinx Zynq-7000 AP SoC based evaluation kits: Xilinx ZC702 and ZC706, MicroZed™ and ZedBoard™ from Avnet Electronics Marketing. Design deliverables include: evaluation logicBRICKS IP cores, hardware design files prepared for Xilinx Vivado or ISE (XPS) design suite, complete Linux OS image, Xylon logicBRICKS software drivers for Linux OS and DirectFB, and demo software applications.

To learn more about the Xylon reference designs, contact Xylon or visit the web:

Email: support@logicbricks.com

URL: http://www.logicbricks.com/logicBRICKS/Reference-logicBRICKS-Design.aspx

# **Ordering Information**

This product is available directly from Xylon under the terms of the Xylon's IP License. Please visit our web shop or contact Xylon for pricing and additional information:

Email: <u>sales@logicbricks.com</u>

URL: <u>www.logicbricks.com</u>

This publication has been carefully checked for accuracy. However, Xylon does not assume any responsibility for the contents or use of any product described herein. Xylon reserves the right to make any changes to product without further notice. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. Xylon products are not intended for use in the life support applications. Use of the Xylon products in such appliances is prohibited without written Xylon approval.

### **Related Information**

### Xilinx Programmable Logic

For information on Xilinx programmable logic or development system software, contact your local Xilinx sales office, or:

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 Phone: +1 408-559-7

Phone: +1 408-559-7778 Fax: +1 408-559-7114 URL: www.xilinx.com

# **Revision History**

| Version | Date          | Note                                                                                   |  |

|---------|---------------|----------------------------------------------------------------------------------------|--|

| 1.00.a  | 06. 03. 2009. | Initial Xylon release – new doc template.                                              |  |

| 1.01.   | 29. 11. 2010. | Updated according to modifications made in the core version 1.01.a.                    |  |

| 1.05.a  | 08. 06. 2011. | Added AXI support.                                                                     |  |

| 1.05.c  | 30. 09. 2011. | Timings statistics update.                                                             |  |

| 1.06.a  | 27. 10. 2011. | Updated according to modifications made in the core version 1.06.a.                    |  |

| 1.06.b  | 15. 12. 2011. | Updated according to modifications made in the core version 1.06.b.                    |  |

| 1.07.   | 30. 01. 2013. | Added support for Artix-7 and Zynq 7000 AP SoC.                                        |  |

| 1.7.    | 09. 12. 2014. | Document updated with information about the Xilinx Vivado compatible logiSDHC IP core. |  |

|         |               | Updated Table 2 and Table 3.                                                           |  |

|         |               | Small corrections made throughout the document.                                        |  |

|         |               | New versioning scheme introduced for Vivado packaged IP core.                          |  |

| Version | Date          | Note                                                                        |

|---------|---------------|-----------------------------------------------------------------------------|

| 2.0.    | 24. 07. 2017. | Updated Table 1 with implementation statistics for the new IP core version. |

|         |               | Removed PLB, OPB and XMB interfaces.                                        |

|         |               | Removed Xylon-Specific DMA support.                                         |

|         |               | Updated Table 2 and Table 3.                                                |

| 2.1.    | 22.12.2017.   | Added support for Xilinx UltraScale and UltraScale+ families.               |

|         |               | Updated example implementation statistics (Table 1) for UltraScale+ family. |

| 2.2.    | 03.12.2018.   | Added support for Spartan 7 family.                                         |

| 2.2.    | 03.10.2019.   | Updated Table 1.                                                            |