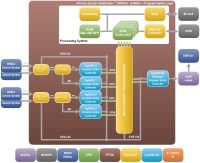

| The logiADAK-VDF-ZU Video Design Framework includes pre-verified logicBRICKS reference designs for video capture from Xylon cameras and the display output under the Linux operating system.  The complete camera-to-display SoC designs, which use just a fraction of available programmable logic, significantly save the design time. Instead of starting from scratch and having to spend months designing and building a new design framework, the logiADAK-VDF-ZU users can immediately focus on specific vision-based parts of their next SoC design. The designs are prepared for the AMD Vivado Design Suite and the AMD Vitis™ Unified Software Platform.  | FOUR-CAM Design

This design implements four parallel video inputs from Xylon cameras and the display output with the RGB overlay. All video inputs are stored in the video memory, and by mean of the on board push buttons, the design user can select each of them for the full screen display output.

Video inputs are controlled by the logiWIN Versatile Video Input IP cores, and the video output is displayed by the logiCVC-ML Compact Multilayer Video Controller IP core.

| | Documentation Read More Related Info External Links Related Products Need Help? Xylon is a member of: |