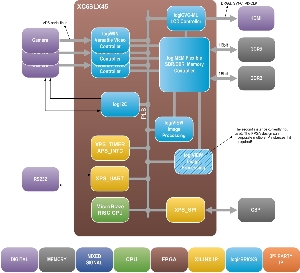

| Xylon's Video Surveillance Multi-Head 360° View Camera demo FPGA design is implemented by logicBRICKS IP cores configured for use with the AMD Spartan™ 6 FPGA. The design is fully compatible with the AMD Platform Studio (XPS) and EDK implementation tools.  FPGA Architecture - Xylon Demo Video Surveillance Multi Head 360 Degrees Camera

(Click to Enlarge)

The reference design includes the AMD MicroBlaze™ soft-CPU, and does not require an external host processor for system control. The presented FPGA design is an sample implementation which can be altered to better suit system requirements, for example the design can be ported to the AMD Zynq™ 7000 and benefit from dual-core ARM® Cortex™-A9 MPCore™ processing system capable to support very advanced video processing algorithms, LVDS inputs can be exchanged by CVBS or Ethernet inputs, etc.

The FPGA controls three HD imagers (cameras) and accepts video data from the imagers through LVDS serial link. The logiWIN Versatile Video Input IP core formats input video streams and stores video frames in dedicated buffers implemented in external DDR2 memory. Synchronization mechanism between all IP cores assures a flicker-free video image.

| The logiVIEW Perspective Transformation and Lens Correction Image Processor is the key IP core. It processes all video inputs within a single video frame. It removes fish-eye lens distortions and than executes the programmed perspective transformations. A single instance of the logiVIEW IP core can support much higher input video resolutions than 1MP used in the current demo. In case that required video input and output resolutions exceed logiVIEW processing capabilities, it is possible to use multiple IP core’s instances to increase FPGA video capabilities by processing parts of video image in parallel. |

All IP cores share a common external memory bank, controlled by the logiMEM_arb memory controller. The memory controller can be programmed in different ways to assure the highest possible memory bandwidth utilization and optimal prioritization between memory requests from different IPs.

The system uses the Secure Digital (SD) card as non-volatile memory controlled by the logiSDHC Host Controller IP core.

The transformed data is further stored in video memory buffers dedicated to the logiCVC-ML Compact Multilayer Video Controller. The logiCVC-ML IP core stitches processed images from all cameras into a single image display.

Xylon offers FPGA design services and can make design changes on request!

| Read more: - Multi Head Camera Introduction - Image Composing - Demo Hardware Read more about Xylon's solutions for the industrial market: - Pedestrian Detection - Operator Panel - Instrumentation | Read More Related Info Related Products Need Help? Xylon is a member of: |